Keith On... Hardware

K.E. Schubert

Founder Renaissance Research Labs

Associate Professor Department of Electrical and Computer Engineering School of Engineering and Computer Science Baylor University

## Contents

| Ι | Electronics                                                                                                                                                                                                                                             | 3                                                                                              |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 1 | Passive Components         1.1       Resistor         1.2       Capacitor         1.3       Inductor         1.4       Memristence                                                                                                                      | <b>5</b><br>5<br>6<br>6                                                                        |

| 2 | Basic Laws         2.1       Coulomb's Law         2.2       Maxwell's Laws         2.2.1       Gauss' Law for Electricity         2.2.2       Gauss' Law for Magnetism         2.2.3       Faraday's Law of Induction         2.2.4       Ampere's Law | 7<br>7<br>8<br>8<br>9<br>9                                                                     |

| 3 | 3.1       Energy Levels         3.2       Intrinsic Semiconductors         3.3       Extrinsic Semiconductors         3.3.1       P Type Semiconductors                                                                                                 | 11<br>11<br>12<br>14<br>14<br>14                                                               |

| 4 |                                                                                                                                                                                                                                                         | <b>17</b><br>17                                                                                |

| 5 | Binary Junction Transistors                                                                                                                                                                                                                             | 19                                                                                             |

| 6 | 6.1 Ideal Behavior                                                                                                                                                                                                                                      | <b>21</b><br>21<br>22                                                                          |

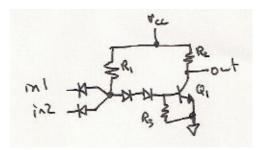

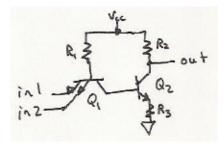

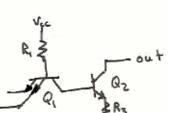

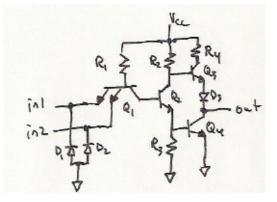

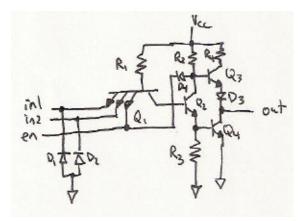

| 7 | 7.1       Diode Logic       7.2         7.2       Resistor Transistor Logic       7.3         7.3       Diode Transistor Logic       7.4         7.4       Transistor Transistor Logic       7.4         7.4.1       Open Collector Outputs       7.4   | <ul> <li>23</li> <li>24</li> <li>24</li> <li>24</li> <li>24</li> <li>24</li> <li>25</li> </ul> |

|          | 7.5<br>7.6                                                                               | 7.4.3 Tristate Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25<br>25<br>25                                                                                             |

|----------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Π        | D                                                                                        | Digital Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                                                                         |

| 8        | Boc<br>8.1<br>8.2<br>8.3                                                                 | <b>Dean Algebra</b> Postulates and Theorems         DeMorgan's Law         Gates                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>31</b><br>31<br>32<br>34                                                                                |

| 9        | Log<br>9.1<br>9.2                                                                        | cic Conventions         Logic-Voltage Conventions         Canonical Forms         9.2.1         Sum of Products         9.2.2         Product of Sums                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>37</li> <li>37</li> <li>42</li> <li>42</li> <li>43</li> </ul>                                     |

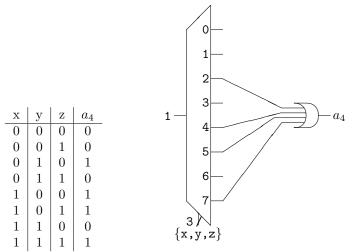

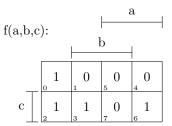

| 11       | 10.1<br>10.2<br>10.3<br><b>Syn</b><br>11.1<br>11.2<br><b>Tim</b><br>12.1<br>12.2<br>12.3 | nbinational Circuits         Designing: Tables         10.1.1 Implementing With Sum of Products         10.1.2 Implementing With Product of Sums         10.1.3 Implementing With Decoders         10.1.4 Implementing With Multiplexors         10.1.4 Implementing With Multiplexors         2 Designing: Karnaugh Maps         3 Quine-McCluskey         counters         9 General Design         ning         Combinational Circuits         9 Sequential Circuits         9 Flip Flops and Hazards         10 How Often? | <b>47</b><br>47<br>48<br>48<br>48<br>49<br>51<br><b>55</b><br>56<br>56<br>56<br>59<br>59<br>59<br>60<br>60 |

| II<br>13 | <b>Cod</b><br>13.1                                                                       | des         Standard Codes         13.1.1 Unsigned         13.1.2 Signed         Huffman Codes                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>63</li> <li>65</li> <li>65</li> <li>67</li> <li>67</li> </ul>                                     |

|          | 13.3                                                                                     | 13.2.1 Huffman Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68<br>68<br>69                                                                                             |

| <b>14</b> | Integ                                                                                                             | ers                                                                                                                                                                                                                                                                                         | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 14.1 I                                                                                                            | nteger numbers                                                                                                                                                                                                                                                                              | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 14.2 A                                                                                                            | Addition                                                                                                                                                                                                                                                                                    | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

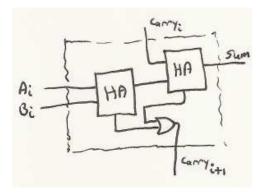

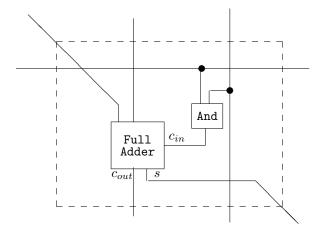

|           | 1                                                                                                                 | 4.2.1 Ripple Adders                                                                                                                                                                                                                                                                         | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1                                                                                                                 | 4.2.2 Conditional Sum                                                                                                                                                                                                                                                                       | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1                                                                                                                 | 4.2.3 Carry-Lookahead                                                                                                                                                                                                                                                                       | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1                                                                                                                 | 4.2.4 Other notes                                                                                                                                                                                                                                                                           | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1                                                                                                                 | 4.2.5 Signed Int                                                                                                                                                                                                                                                                            | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1                                                                                                                 | 4.2.6 2's Comp                                                                                                                                                                                                                                                                              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1                                                                                                                 | 4.2.7 Excess                                                                                                                                                                                                                                                                                | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

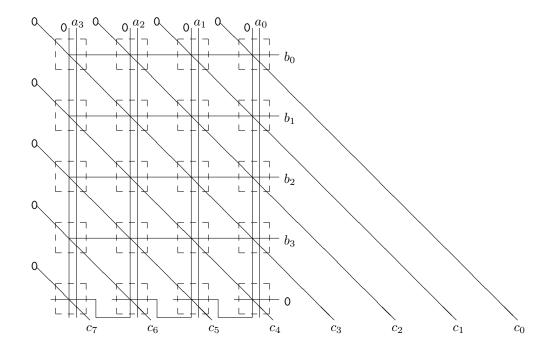

|           | 14.3 I                                                                                                            | $Multiplication \ldots \ldots$                                                                                                                                       | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1                                                                                                                 | 4.3.1 unsigned                                                                                                                                                                                                                                                                              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 1                                                                                                                 | 4.3.2 2's complement                                                                                                                                                                                                                                                                        | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

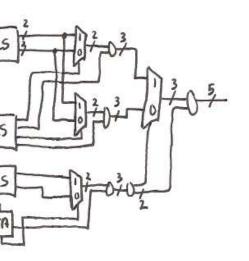

|           | 1                                                                                                                 | 4.3.3 Systolic Array                                                                                                                                                                                                                                                                        | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 14.4 I                                                                                                            | ntegrated Examples                                                                                                                                                                                                                                                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 14.5 I                                                                                                            | Residue Arithmetic                                                                                                                                                                                                                                                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |                                                                                                                   |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15        |                                                                                                                   | 0                                                                                                                                                                                                                                                                                           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |                                                                                                                   |                                                                                                                                                                                                                                                                                             | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |                                                                                                                   | 0                                                                                                                                                                                                                                                                                           | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |                                                                                                                   |                                                                                                                                                                                                                                                                                             | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |                                                                                                                   | 0 11 0                                                                                                                                                                                                                                                                                      | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

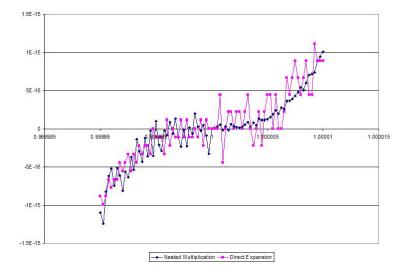

|           | 15.5 I                                                                                                            | Evaluating a Polynomial                                                                                                                                                                                                                                                                     | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |                                                                                                                   |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IV        | O O                                                                                                               | rganization 9                                                                                                                                                                                                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |                                                                                                                   |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

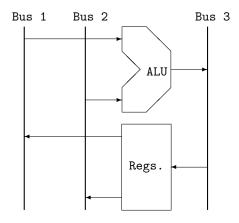

| 16        |                                                                                                                   | 1                                                                                                                                                                                                                                                                                           | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |